線上影音

Home > ANSYS SIwave教學> Via Stub Effect

本文始於2009以SIwave v3.5+Designer/Nexxim v4.0完成操作,2014年重新撰寫,以SIwave 2014將模擬結果更新,介紹貫孔的stub與NFP (Non-Functional Pad)效應。The article started in 2009 with SIwave v3.5+Designer v4.0, and is revised on 2011, 2014, and 2016 with SIwave2014. It is intended to introduce stub and NFP (Non-Functional Pad) effect.

-

問題與討論

8.1 頻寬多少,才需要在意Via Stub Effect?

8.2 除了背鑽外,還有什麼方法可以改善via stub effect?

8.3 如何在SIwave內比較有無NFP (Non-Functional Pad)的差異?

8.4 SIwave如何模擬背鑽的過孔? How does SIwave simulate the backdrilled via?

8.5 via stub電容效應除了如本文所示影響S參數共振點位置、影響TDR外,如何影響眼圖?

8.6 一般via barrel的電容與電感效應是隨著板厚降低而降低,但via stub的電容效應也是如此嗎?

8.7 Via Stub effect是電容效應;100mils以上的板厚,速度3.125GHz就需要考慮stub effect 嗎?

![]()

在"Via的貫孔效應"分析後發現,針對Via Stub Effect還有些地方需要確認

-

Alter AN315 (p.14~15):Via Stub effect是電容效應,且板厚100mils以內,速度3.125GHz以下者不需要背鑽 ??

-

一般via barrel的電容與電感效應是隨著板厚降低而降低,但via stub的電容效應也是如此嗎?

-

頻寬多少,才需要在意Via Stub Effect?

設計以下幾個實驗

1.1 堆疊的設計如下所示,配合線寬10mils,讓內外層走線的特性阻抗都維持50歐姆

1.2 先保留每一層的pad,Non-Functional Pad (NFP),hole size radius=10mils、pad size=10mils,and anti-pad=10mils

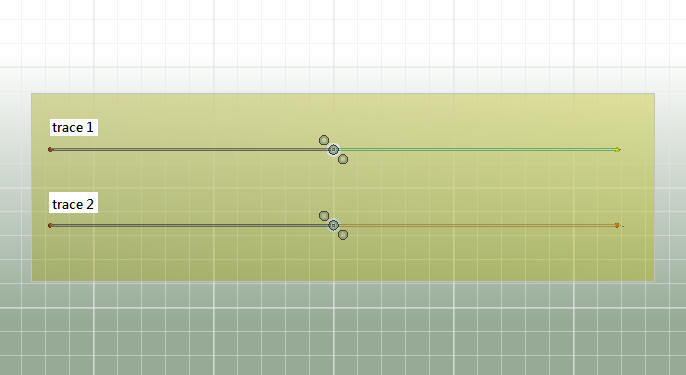

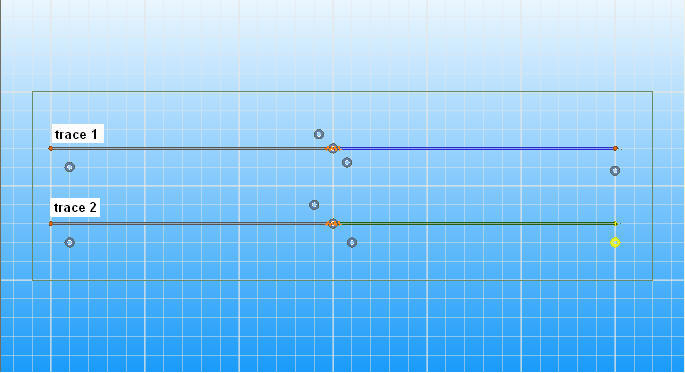

1.3 Trace 1走layer1 to layer4,Trace 2走layer1 to layer6,線長60mm

1.4 SIwave的S21(Insertion Loss):3GHz以內差異不大,3~35GHz以沒有stub的Trace 2明顯較好

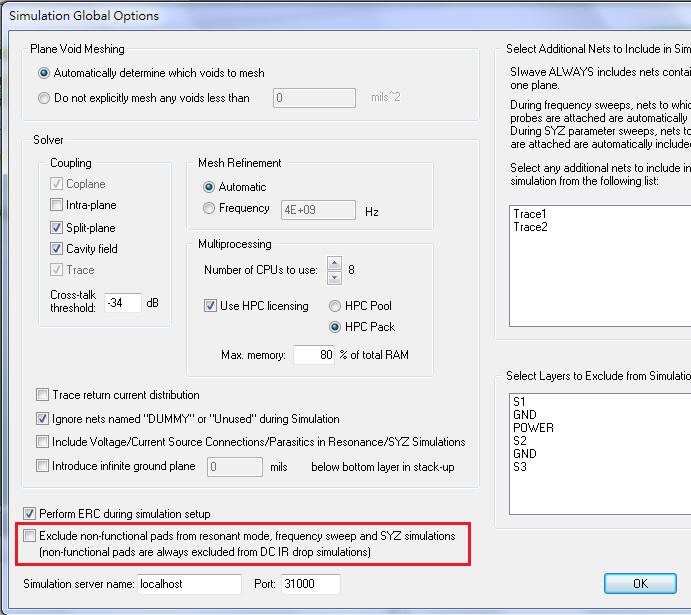

To run this step, please confirm the [Exclude non-functional pads from ...] item in SIwave options is uncheck at the first.

1.5 SIwave的TDR:rise time of step pulse is 30ps, Interpolating Sweep 50GHz

Trace 1過via後改走layer4,線寬不變,但離reference plane的距離變遠了,故特性阻抗略變大49.7 -> 50.5

1.6 下圖是Trace 1, 2在Tr=100ps時的TDR。可看出波形抖動幅度較上圖緩,表示0.5/100p=5GHz的訊號走過via相對於0.5/30p=16.6GHz的訊號 走過via,感受到的傳輸線上特性阻抗落差(不連續性)較小。

2.1 堆疊的設計如下所示,配合線寬20mils,讓內外層走線的特性阻抗都維持50歐姆

2.2 SIwave的S21(Insertion Loss):20GHz以內,以沒有stub的Trace 2表現較好。但20GHz以上 ,Trace 1反而較好,此時是被loop inductance dominate

To run this step, please confirm the [Exclude non-functional pads from ...] item in SIwave options is uncheck at the first.

2.3 SIwave的TDR: Trace 2的via電容效應明顯比Trace 1小。(rise time of step pulse is 30ps, Interpolating Sweep 50GHz)

與48mils板厚的情況相比,此時Trace 1電容效應增加許多,這可以藉著去除NFP改善。

Trace1在800ps~1200ps這段的TDR彈到52 ohm,應該是Trace1經過via後走內層導致特性阻抗偏離50 ohm所造成的。如果把時間軸往後延伸會發現象是多次反射的震盪

2.4 To check the [Exclude non-functional pads from ...] item in SIwave options, then the result will be

3.1 堆疊的設計如下所示,配合線寬10mils,讓內外層走線的特性阻抗都維持50歐姆

3.2 Trace 1走layer1 to layer5,Trace 2走layer1 to layer12。 (因為層數較多,多打幾個GND vias)

3.3 SIwave的S21(Insertion Loss):3GHz以內,Trace1、Trace2差不多,3G~12GHz則以Trace2較好,12GHz以上Trace1反而好。

Trace 1的S21在8.1G的下拉共振點,就是stub effect造成的

3.4 SIwave的TDR: (rise time of step pulse is 30ps, Interpolating Sweep 50GHz)

4.1 堆疊的設計如下所示,配合線寬20mils,讓內外層走線的特性阻抗都維持50歐姆

4.2 SIwave的S21(Insertion Loss):3GHz以內,Trace1、Trace2差不多;3G~8GHz以Trace2較好,8GHz以上Trace1較好。

Trace 1的S21在5G的下拉共振點,就是stub effect造成的

4.3 SIwave的TDR: (rise time of step pulse is 30ps, Interpolating Sweep 50GHz)

當板厚<100mils時,因為length of barrel is shorter,via引入的串聯電感效應較輕微,此時在意stub電容效應大於via barrel的電感效應。

當板厚>100mils時,串聯電感效應與stub對SI都有一定的影響。S21在0~12GHz是沒有stub effect的trace2較好,但在12G~50GHz則是以有stub但串聯電感效應較小的trace1較好。

故隨著板厚的增加,stub effect並沒有改善,也是變嚴重。

同樣的堆疊與貫孔結構,只要換層via有留stub,寄生電容效應就會增加,故可以確定via stub effect確實是電容效應,其主要是stub part of via barrel對於power/ground plane所形成的寄生電容效應。降低貫孔電容效應的方法,也都可以改善via stub effect:包括縮小pad size、加大anti-via、去掉NFP。

via barrel結構上,訊號經過的部份貢獻串聯電感效應,而訊號沒經過的部分(stub)貢獻電容效應,這兩者是相互trade-off的。板厚<100mils時,via stub電容效應影響較大,盡量縮短stub長度;板厚>100mils時,via電感效應較大,此時就以降低寄生電感為優先,stub相對遺留就長了些。以上是就本文所示的結構所歸納出來的設計原則,面對不同板子與頻寬的考慮,可能有其他因素需要互相取捨,實際的設計原則還是透過模擬觀察時域與頻域的特性來決定。

-

問題與討論

8.1 頻寬多少,才需要在意Via Stub Effect?

Ans : 不管板厚多少,頻寬3GHz以內是不太需要考慮stub effect的。

8.2 除了背鑽外,還有什麼方法可以改善via stub effect?

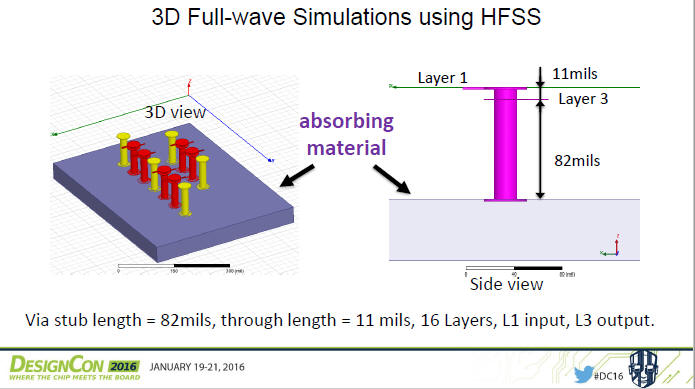

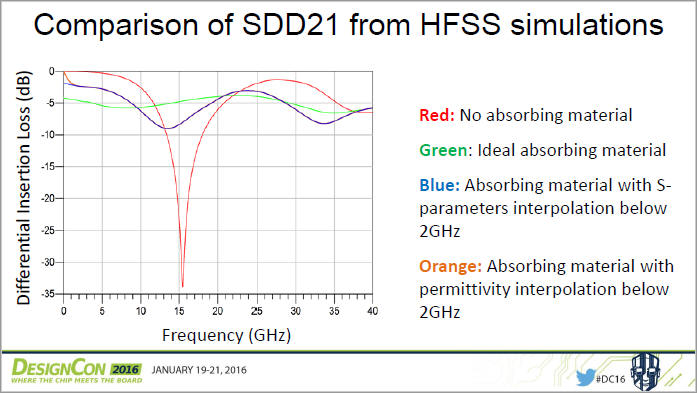

Ans : Intel在2016於DesignCon發表了一篇用HFSS研究的paper,以在PCB表面放一層厚的吸收介質(蓋在stub端的via上),可以有效的降低via stub [5]

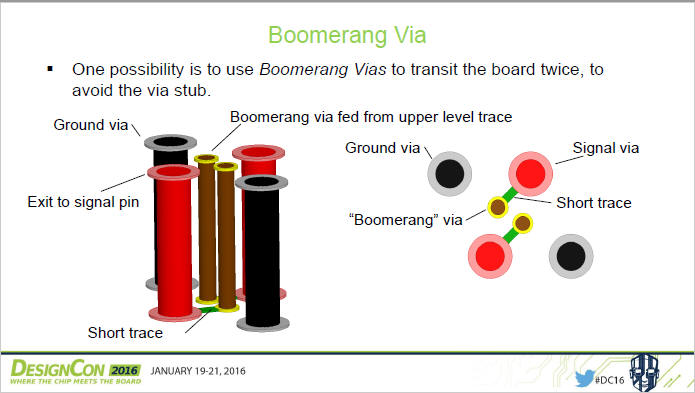

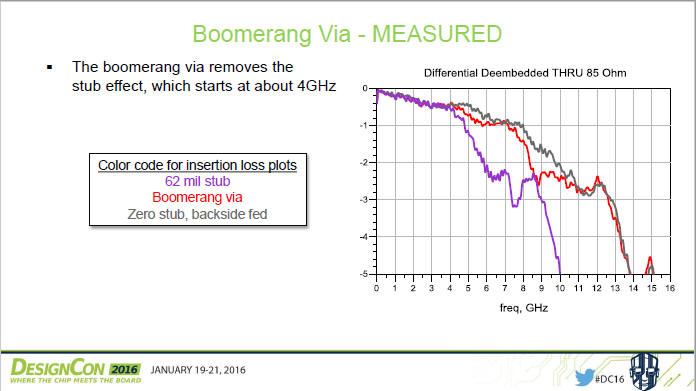

Intel在2016於DesignCon發表了 另一篇用HFSS研究的paper,加boomerang via (Intel專利US7501586 B2),可以有效的降低via stub effect [6], p66

8.3 如何在SIwave內比較有無NFP (Non-Functional Pad)的差異?

Ans : 有兩個方法可以在SIwave內比較有無NFP。第一個方法是直接在SIwave options設定內選擇是否要考慮NFP此option [Exclude non-functional pads from ...] as step 2.4,另一個方法是改via pad-stack as step 5, 6。由於SIwave set [Exclude non-functional pads from ...] by default, 所以容易讓user誤以為在via padstack內remove NFP沒有作用。

8.4 SIwave如何模擬背鑽的過孔? How does SIwave simulate the backdrilled via?

Ans:It is a bit tricky. To simulate backdrilled via, you have to set [Bottom Layer] of via property, NOT modify via definition in [Edit Padstacks].

It works for HFSS region in R19.x SIwave as well.

8.5 via stub電容效應除了如本文所示影響S參數共振點位置、影響TDR外,如何影響眼圖?

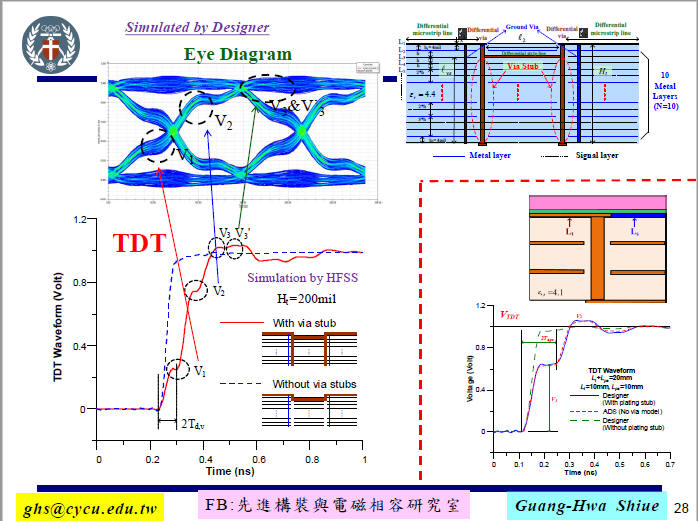

Ans : 夠長的via stub,對高速訊號來說,就像是傳輸線上分支出來的一條尾巴(像電鍍線plating stub),會在較長的傳輸線上引起反射,導致眼圖的上升緣或下降緣出現階梯狀。下圖為中原大學薛教授的講義

8.6 一般via barrel的電容與電感效應是隨著板厚降低而降低,但via stub的電容效應也是如此嗎?

Ans : 是的。並且降低貫孔電容效應的方法,也都可以改善via stub effect:包括縮小pad size、加大anti-pad、去掉NFP。

8.7 Alter AN315 (p.15):Via Stub effect是電容效應;100mils以上的板厚,速度3.125GHz就要考慮stub effect 嗎?

Ans : 100mils以上的板厚,速度3.125GHz,via stub影響還不明顯,但3.1G以上就開始有影響了。如本文step 3.3所示。

板子不厚或頻寬10GHz以上時,via barrel的電感效應 可能會比stub effect影響大,所以不能只顧縮小stub長度而讓訊號通過的via barrel長度增加,如本文step 2.2 and step 3.3所示,或本站DDR4 Design optimize 2.4.1所示。

綜上所述,較厚的高速板子(厚度接近或超過100mils),建議採用較小via barrel長度配合背鑽的方式進行。至於厚度較薄(6~8 layers)的高速板子,同樣是不背鑽,採用較小via barrel長度的走線設計"有可能"會比採用較長via barrel長度的走線設計的方式來的好。

[1] Altera "AN529:Via Optimization for High-Speed Designs"

[2] Altera Technical Brief:High-Speed Board Design Advisor High-Speed Channel Design and Layout, p.3

[3] http://www.signalintegrity.com/Pubs/edn/StubTermination.htm

[4] Via Stube Study, DesignCon 2009

Altera design rule:keep dangling stub < 50mils。(無關於板厚與頻寬)

[5] Shaowu Huang, Kai Xiao, "Electromagnetic Wave Absorption Technology for Stub Effects Mitigation", Intel Corp., DesignCon 2016 .

[6] Timothy Wig, Steve Krooswyk, "Gen 4 PCIe Connector & Channel Design and Optimization: 16GT/s for Free", Intel Corp., DesignCon 2016